Verilog Blocking & Non-Blocking

Blocking assignment statements are assigned using = and are executed one after the other in a procedural block. However, this will not prevent execution of statments that run in a parallel block.

Note that there are two initial blocks which are executed in parallel when simulation starts. Statements are executed sequentially in each block and both blocks finish at time 0ns. To be more specific, variable a gets assigned first, followed by the display statement which is then followed by all other statements. This is visible in the output where variable b and c are 8'hxx in the first display statement. This is because variable b and c assignments have not been executed yet when the first $display is called.

In the next example, we'll add a few delays into the same set of statements to see how it behaves.

Non-blocking

Non-blocking assignment allows assignments to be scheduled without blocking the execution of following statements and is specified by a symbol. It's interesting to note that the same symbol is used as a relational operator in expressions, and as an assignment operator in the context of a non-blocking assignment. If we take the first example from above, replace all = symobls with a non-blocking assignment operator , we'll see some difference in the output.

See that all the $display statements printed 'h'x . The reason for this behavior lies in the way non-blocking assignments are executed. The RHS of every non-blocking statement of a particular time-step is captured, and moves onto the next statement. The captured RHS value is assigned to the LHS variable only at the end of the time-step.

So, if we break down the execution flow of the above example we'll get something like what's shown below.

Next, let's use the second example and replace all blocking statements into non-blocking.

Once again we can see that the output is different than what we got before.

If we break down the execution flow we'll get something like what's shown below.

Blocking vs. Nonblocking in Verilog

The concept of Blocking vs. Nonblocking signal assignments is a unique one to hardware description languages. The main reason to use either Blocking or Nonblocking assignments is to generate either combinational or sequential logic. In software, all assignments work one at a time. So for example in the C code below:

The second line is only allowed to be executed once the first line is complete. Although you probably didn’t know it, this is an example of a blocking assignment. One assignment blocks the next from executing until it is done. In a hardware description language such as Verilog there is logic that can execute concurrently or at the same time as opposed to one-line-at-a-time and there needs to be a way to tell which logic is which.

<= Nonblocking Assignment

= Blocking Assignment

The always block in the Verilog code above uses the Nonblocking Assignment, which means that it will take 3 clock cycles for the value 1 to propagate from r_Test_1 to r_Test_3. Now consider this code:

See the difference? In the always block above, the Blocking Assignment is used. In this example, the value 1 will immediately propagate to r_Test_3 . The Blocking assignment immediately takes the value in the right-hand-side and assigns it to the left hand side. Here’s a good rule of thumb for Verilog:

In Verilog, if you want to create sequential logic use a clocked always block with Nonblocking assignments. If you want to create combinational logic use an always block with Blocking assignments. Try not to mix the two in the same always block.

Nonblocking and Blocking Assignments can be mixed in the same always block. However you must be careful when doing this! It’s actually up to the synthesis tools to determine whether a blocking assignment within a clocked always block will infer a Flip-Flop or not. If it is possible that the signal will be read before being assigned, the tools will infer sequential logic. If not, then the tools will generate combinational logic. For this reason it’s best just to separate your combinational and sequential code as much as possible.

One last point: you should also understand the semantics of Verilog. When talking about Blocking and Nonblocking Assignments we are referring to Assignments that are exclusively used in Procedures (always, initial, task, function). You are only allowed to assign the reg data type in procedures. This is different from a Continuous Assignment . Continuous Assignments are everything that’s not a Procedure, and only allow for updating the wire data type.

Leave A Comment Cancel reply

Save my name, email, and website in this browser for the next time I comment.

Procedural Assignments

Blocking assignments, race around condition: a problem with blocking assignment.

- Support email is [email protected] .

- Playgrounds

Languages & Libraries

tools & simulators, examples, community.

- testbench.sv

(drag and drop anywhere)

(Allowed extensions: jpg, jpeg, png, svg)

(Allowed extensions: mp4)

Available Apps

- EDA Playground

EPWave Examples

- Trivial Example

- RAM from EDA Playground

- OpenCores Example

Validation Error

User validation required.

Your account is not validated. If you wish to use commercial simulators, you need a validated account. If you have already registered (or have recently changed your email address), but have not clicked on the link in the email we sent you, please do so. If you cannot find the email, please check your spam/junk folder. Or click here to resend the email. If you have not already registered for a full account, you can do so by clicking below. You will then need to provide us with some identification information. You may wish to save your code first .

Not Supported During Collaboration

Creating, deleting, and renaming files is not supported during Collaboration. To encourage development of these features for Collaboration, tweet to @EDAPlayground

Please Log In

Please save.

This playground may have been modified. Please save or copy before starting collaboration.

Share Your Playground

Submit your exercise.

Your exercise has been submitted.

Blocking and Non-blocking Assignment in Verilog

- Assignment is only done in procedural block(always ot initial block)

- Both combintational and sequential circuit can be described.

- Assignment can only possible to reg type irrespect of circuit type

Let's say we want to describe a 4-bit shift register in Verilog. For this, we are required to declare a 3-bit reg type variable.

The output of shift[0] is the input of shift[1], output of shift[1] is input of shift[2], and all have the same clock. Let's complete the description using both assignment operator.

Non-Blocking Assignment

When we do synthesis, it consider non-blocking assignment separately for generating a netlist. If we see register assignment in below Verilog code, all register are different if we consider non-blocking assignment separately. If you do the synthesis, it will generate 3 registers with three input/output interconnects with a positive edge clock interconnect for all register. Based on the Verilog description, all are connected sequentially because shift[0] is assigned d, shift[1] is assigned shift[0], and shift[2] is assigned shift[1].

Blocking Assignment

If we use blocking assignment and do the syhtheis, the synthesis tool first generate netlist for first blocking assignment and then go for the next blocking assignment. If in next blocking assignment, if previous output of the register is assigned to next, it will generate only a wire of previously assigned register.

In below Verilog code, even though all looks three different assignment but synthesis tool generate netlist for first blocking assigment which is one register, working on positive edge of clock, input d and output shift[0]. Since blocking assignment is used, for next blocking assignment, only wire is generated which is connected to shift[0]. Same is for next statement a wire is generated which is connected to shift[0].

Click like if you found this useful

Add Comment

This policy contains information about your privacy. By posting, you are declaring that you understand this policy:

- Your name, rating, website address, town, country, state and comment will be publicly displayed if entered.

- Your IP address (not displayed)

- The time/date of your submission (displayed)

- Administrative purposes, should a need to contact you arise.

- To inform you of new comments, should you subscribe to receive notifications.

- A cookie may be set on your computer. This is used to remember your inputs. It will expire by itself.

This policy is subject to change at any time and without notice.

These terms and conditions contain rules about posting comments. By submitting a comment, you are declaring that you agree with these rules:

- Although the administrator will attempt to moderate comments, it is impossible for every comment to have been moderated at any given time.

- You acknowledge that all comments express the views and opinions of the original author and not those of the administrator.

- You agree not to post any material which is knowingly false, obscene, hateful, threatening, harassing or invasive of a person's privacy.

- The administrator has the right to edit, move or remove any comment for any reason and without notice.

Failure to comply with these rules may result in being banned from submitting further comments.

These terms and conditions are subject to change at any time and without notice.

Comments (1)

hey in blocking assignment do we get shift in data i dont think so . we get all values same and equal to d.

Please do not focus on the module name; focus on how the netlist is generated after the synthesis.

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

| ||

| Blocking and Nonblocking Statements | ||

| ||

: A blocking statement must be executed before the execution of the statements that follow it in a sequential block. In the example below the first time statement to get executed is a = b followed by | ||

| ||

| ||

: Nonblocking statements allow you to schedule assignments without blocking the procedural flow. You can use the nonblocking procedural statement whenever you want to make several register assignments within the same time step without regard to order or dependence upon each other. It means that nonblocking statements resemble actual hardware more than blocking assignments. | ||

| ||

| block_nonblock(); 2 a, b, c, d , e, f ; 3 4 5 6 a #10 1'b1; 7 b #20 1'b0; 8 c #40 1'b1; 9 10 11 12 13 d 1'b1; 14 e 1'b0; 15 f 1'b1; 16 17 18 | ||

| ||

| ||

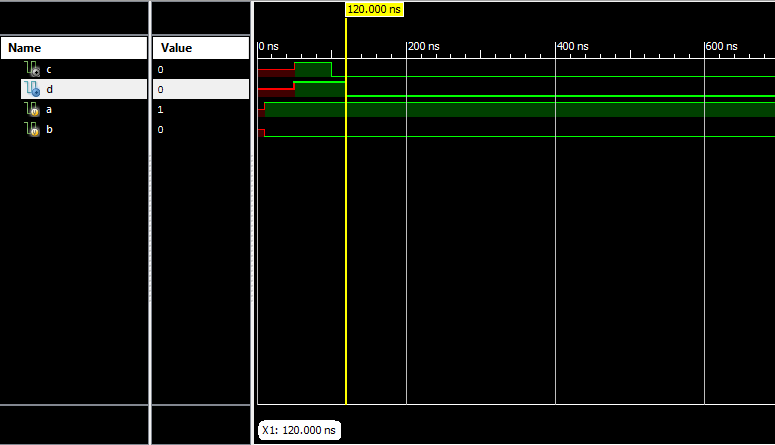

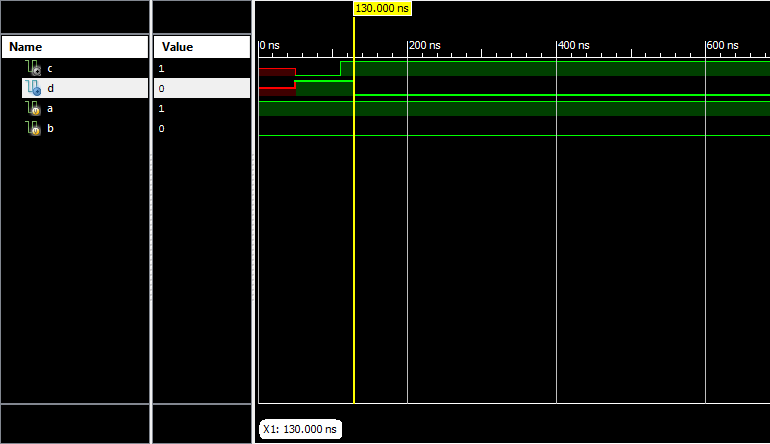

| Example - Blocking | ||

| ||

| blocking (clk,a,c); 2 clk; 3 a; 4 c; 5 6 clk; 7 a; 8 c; 9 b; 10 11 ( clk ) 12 13 b a; 14 c b; 15 16 17 | ||

| ||

| ||

| ||

| ||

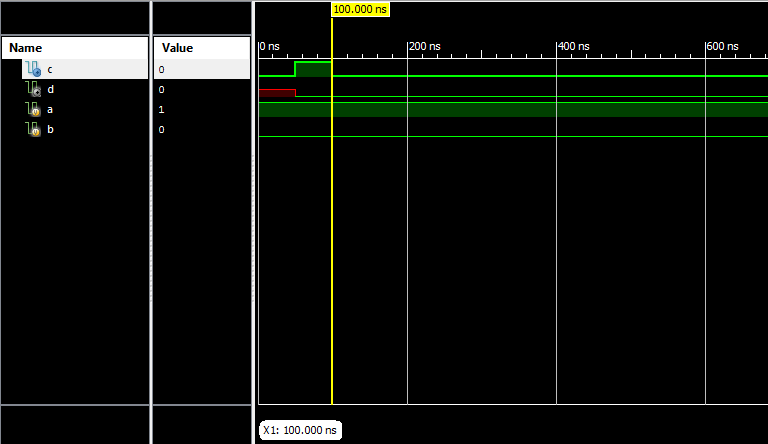

| Example - Nonblocking | ||

| ||

| nonblocking (clk,a,c); 2 clk; 3 a; 4 c; 5 6 clk; 7 a; 8 c; 9 b; 10 11 ( clk ) 12 13 b a; 14 c b; 15 16 17 | ||

| ||

| ||

| ||

| ||

| ||

| ||

|

|

|

|

|

|

|

|

|

|

|

Stack Exchange Network

Stack Exchange network consists of 183 Q&A communities including Stack Overflow , the largest, most trusted online community for developers to learn, share their knowledge, and build their careers.

Q&A for work

Connect and share knowledge within a single location that is structured and easy to search.

Difference between blocking and nonblocking assignment Verilog

I was reading this page http://www.asic-world.com/verilog/verilog_one_day3.html when I came across the following:

We normally have to reset flip-flops, thus every time the clock makes the transition from 0 to 1 (posedge), we check if reset is asserted (synchronous reset), then we go on with normal logic. If we look closely we see that in the case of combinational logic we had "=" for assignment, and for the sequential block we had the "<=" operator. Well, "=" is blocking assignment and "<=" is nonblocking assignment. "=" executes code sequentially inside a begin / end, whereas nonblocking "<=" executes in parallel.

I was fairly sure that nonblocking assignments were sequential while blocking assignments were parallel. After all, you can make blocking assignments with assign statements outside of always blocks, and those all run in parallel. Is this a mistake, or is the behavior different inside an always block? And, if the behavior IS different inside an always block, can nonblocking assignments be made outside an always block?

3 Answers 3

was fairly sure that nonblocking assignments were sequential while blocking assignments were parallel.

Blocking assignment executes "in series" because a blocking assignment blocks execution of the next statement until it completes. Therefore the results of the next statement may depend on the first one being completed.

Non-blocking assignment executes in parallel because it describes assignments that all occur at the same time. The result of a statement on the 2nd line will not depend on the results of the statement on the 1st line. Instead, the 2nd line will execute as if the 1st line had not happened yet.

- \$\begingroup\$ So what about assign statements? Are they just in a whole class of their own? \$\endgroup\$ – Void Star Commented Nov 24, 2013 at 4:25

- 6 \$\begingroup\$ Yes, assign statements occur outside of always blocks and are generally used to describe to combinatorial (un-latched) logic (while always blocks, with some exceptions, describe sequential logic). AFAIK, assign statements always execute "in parallel" whenever their LHS has a value change. \$\endgroup\$ – The Photon Commented Nov 24, 2013 at 4:28

- \$\begingroup\$ Okay... I'm starting to get the impression that Verilog just isn't the most elegantly designed language. This is gonna be like learning C was. \$\endgroup\$ – Void Star Commented Nov 24, 2013 at 5:30

- 2 \$\begingroup\$ Verilog was designed to "describe" hardware that already exists. Using it as a language to design (synthesize) hardware is a hack. \$\endgroup\$ – The Photon Commented Nov 24, 2013 at 6:02

- 6 \$\begingroup\$ if Verilog "like learning C" is a problem, take a look at VHDL. Some people have fairly strong preferences for one or the other. To some, VHDL is just too verbose. To me, it's much better thought out. (signal/variable assignment semantics are much clearer than blocking/non for example). stackoverflow.com/questions/13954193/… and sigasi.com/content/vhdls-crown-jewel You may prefer it or hate it. But it's worth a look. \$\endgroup\$ – user16324 Commented Nov 24, 2013 at 10:20

Assign statements are neither "blocking" or "nonblocking", they are "continuous". The output of an assign statement is always equal to the specified function of it's inputs. "blocking" and "nonblocking" assignments only exist within always blocks.

A blocking assignment takes affect immediately it is processed. A nonblocking assignment takes place at the end of processing the current "time delta".

always blocks can be used to model either combinatorial or sequential logic (systemverilog has always_comb and always_ff to make this explicit). When modeling combinatorial logic it's usually more efficient to use = but it typically doesn't really matter.

When modelling sequential logic (e.g. always @(posedge clk) ) you normally use nonblocking assingments. This allows you to deterime the "state after the clock edge" in terms of "the state before the clock edge".

It is sometimes useful to use blocking assignments in sequential always blocks as "variables". If you do this then there are two key rules to bear in mind.

- Do not access a reg that is set with blocking assignments inside a sequential always block from outside the always block it is assigned in.

- Do not mix blocking and nonblocking assignments to the same reg.

Breaking these rules is likely to result in synthesis failures and/or behaviour differences between simulation and synthesis.

- \$\begingroup\$ ""Do not access a reg that is set with blocking assignments inside a sequential always block from outside the always block it is assigned in."" Can you please explain it? \$\endgroup\$ – user125575 Commented Oct 4, 2016 at 6:44

- 2 \$\begingroup\$ Different sequential always blocks do not have a defined order. So reading a "reg" set with a blocking assingment in one always block from another always block will lead to unpredicable behaviour. \$\endgroup\$ – Peter Green Commented Oct 4, 2016 at 15:23

- \$\begingroup\$ And even if it appears to work in simulation, a synthesis tool should look at that and say "nope". I use local regs for those intermediate vars, and make sure that they are always assigned to on every clock before being read, so that no 'storage' is implied. \$\endgroup\$ – greggo Commented Mar 30, 2017 at 11:57

- \$\begingroup\$ IIRC at least in quartus it is only considered a warning not an error. \$\endgroup\$ – Peter Green Commented Mar 30, 2017 at 11:59

- \$\begingroup\$ You should not be using nonblocking assignment in combinational logic, it can lock up the simulation. For more details, refer this answer: electronics.stackexchange.com/a/506047/238188 \$\endgroup\$ – Shashank V M Commented Oct 5, 2020 at 14:55

The term Blocking assignment confuses people because the word blocking would seem to suggest time-sequential logic. But in synthesized logic it does not mean this , because everything operates in parallel .

Perhaps a less confusing term would be immediate assignment , which would still differentiate the intermediate results of combinational logic from the inputs to non-transparent memory elements (for example clocked registers), which can have delayed assignment .

From a legalistic standpoint, it all works out very nicely. You can, in fact, consider the = to be a blocking (time-sequential) operation even within always_comb sequences. However, the distinction between time-sequential and parallel makes absolutely no difference in this case because the always_comb block is defined to repeat until the instruction sequence converges on a stable state -- which is exactly what the hardware circuitry will do (if it meets the timing requirements).

The synthesizable subset of Verilog (and especially SystemVerilog) is extremely simple and easy to use -- once you know the necessary idioms. You just have to get past the clever use of terminology associated with the so-called behavioral elements in the language.

- \$\begingroup\$ In behavioral coding styles ( as compared to RTL ), the distinction between blocking and non-blocking can be relevant. In some cases, the synthesis tool may be able to infer functionally equivalent RTL from behavioral component designs. \$\endgroup\$ – Brent Bradburn Commented Jul 21, 2015 at 17:28

- \$\begingroup\$ Of course the procedural mode of SystemVerilog, applicable especially to initial statements within program blocks, uses (time-sequential) blocking assignment exclusively. This is useful for testbench design, but generally not for RTL specification. \$\endgroup\$ – Brent Bradburn Commented Dec 18, 2015 at 18:58

Your Answer

Sign up or log in, post as a guest.

Required, but never shown

By clicking “Post Your Answer”, you agree to our terms of service and acknowledge you have read our privacy policy .

Not the answer you're looking for? Browse other questions tagged verilog or ask your own question .

- Featured on Meta

- Site maintenance - Tuesday, July 23rd 2024, 8 PM - Midnight EST (3 AM - 7 AM...

- Announcing a change to the data-dump process

- Upcoming initiatives on Stack Overflow and across the Stack Exchange network...

Hot Network Questions

- Why are the categories of category theory called "category"?

- Who were the oldest US Presidential nominees?

- Braille-based Base64

- ID a book about siblings forced to become part of evil family and take care of dragons

- How to buy train ticket for bike from Udine (IT) to Villach (AT)

- Why is the future perfect used in "This latest setback will have done nothing to quell the growing doubts about the future of the club."?

- Particles and fields

- What is this huge mosquito looking insect?

- Could an investor sue the CEO or company for not delivering on promised technological breakthroughs?

- The shortest way from A1 to B1

- FDA regulation of end user non-medical software

- Can trusted timestamping be faked by altering some bytes within the document?

- “Redundant” morning blessing?

- Variety without a compactification whose complement is smooth

- Applying a voltage by DAC to a Feedback pin of a DC-DC controller

- Why does my GOV.UK IHS Surcharge keep Declining

- Is "avoid extra null pointer risk" a reason to avoid "introduce parameter objects"?

- How do I rotate curved text 90 degrees around the face of a coin?

- How do people print text on GUI on Win3.1/95/98/... before Win2000?

- EMI shields: When to use 2-piece cap+frame, just a frame, or just a shield (or just a cap)?

- Is there anyway a layperson can discern what is true news vs fake news?

- Probability for a random variable to exceed its expectation

- Is a stiff chain after hot wax application a sign of a correct wax application?

- Have hydraulic shift systems been developed?

Blocking (immediate) and Non-Blocking (deferred) Assignments in Verilog

There are Two types of Procedural Assignments in Verilog.

- Blocking Assignments

- Nonblocking Assignments

To learn more about Delay: Read Delay in Assignment (#) in Verilog

Blocking assignments

- Blocking assignments (=) are done sequentially in the order the statements are written.

- A second assignment is not started until the preceding one is complete. i.e, it blocks all the further execution before it itself gets executed.

Non-Blocking assignments

- Nonblocking assignments (<=), which follow each other in the code, are started in parallel.

- The right hand side of nonblocking assignments is evaluated starting from the completion of the last blocking assignment or if none, the start of the procedure.

- The transfer to the left hand side is made according to the delays. An intra- assignment delay in a non-blocking statement will not delay the start of any subsequent statement blocking or non-blocking. However normal delays are cumulative and will delay the output.

- Non-blocking schedules the value to be assigned to the variables but the assignment does not take place immediately. First the rest of the block is executed and the assignment is last operation that happens for that instant of time.

To learn more about Blocking and Non_Blocking Assignments: Read Synthesis and Functioning of Blocking and Non-Blocking Assignments

The following example shows interactions between blocking and non-blocking for simulation only (not for synthesis).

For Synthesis (Points to Remember):

- One must not mix “<=” or “=” in the same procedure.

- “<=” best mimics what physical flip-flops do; use it for “always @ (posedge clk..) type procedures.

- “=” best corresponds to what c/c++ code would do; use it for combinational procedures.

Spread the Word

- Click to share on Facebook (Opens in new window)

- Click to share on Twitter (Opens in new window)

- Click to share on LinkedIn (Opens in new window)

- Click to share on Pinterest (Opens in new window)

- Click to share on Tumblr (Opens in new window)

- Click to share on Pocket (Opens in new window)

- Click to share on Reddit (Opens in new window)

- Click to email a link to a friend (Opens in new window)

- Click to print (Opens in new window)

Related posts:

- Synthesis and Functioning of Blocking and Non-Blocking Assignments.

- Delay in Assignment (#) in Verilog

- Ports in Verilog Module

- Module Instantiation in Verilog

Post navigation

Leave a reply cancel reply.

Your email address will not be published. Required fields are marked *

Save my name, email, and website in this browser for the next time I comment.

Notify me of follow-up comments by email.

Notify me of new posts by email.

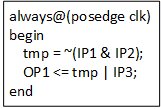

Verilog Blocking & Non-Blocking assignments elaborated

- Post author By Kevin

- Post date 20 October 2020

Blocking / Non-Blocking assignment rules

The main reason to use either Blocking or Non-Blocking assignments is to generate either combinational or sequential logic.

In non-blocking assignments (<=), all registers inside the always block are updated at the end. In blocking assignments (=), the registers are updated immediately.

Whether or not a flip-flop is inferred from a blocking assignment depends on whether or not the value of the variable being assigned needs to be remembered from one clock edge to the next.

It is good practice to separate combinational and sequential code as much as possible. In verilog, if we want to create sequential logic can use a clocked always block with non-blocking assignments. If on the other hand we want to create combinational logic can use an always block with blocking assignments. Best not to mix the two in the same always block but if they are mixed, need to be careful when doing this. Its up to the synthesis tools to determine whether a blocking assignment within a clocked always block will infer a flip-flop or not. If the signal is read before being assigned (eg fig2 below), the tools will infer sequential logic.

For simplicity purposes only showing in the verilog examples below the Always Block. These Always blocks are blocks of sequential logic since it involves a clock.

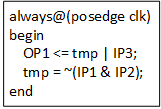

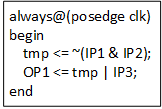

If on an active clock edge, the variable tmp is being assigned a value before it’s value is used (ie ‘write before read’ case) then no flip-flop is required & synthesis will not infer it as shown in fig1 below.

If the value of the reg is used before a new value is assigned to it (ie ‘read before write’ case), then the value that is used will be the value that was assigned on a previous clock. Therefore a flip-flop is required here as shown in fig2 below.

If all non-blocking assignments are used within the always block, it will look like :

Non-blocking assignments always imply flip-flops (order of assignments doesn’t matter). Same block diagram is inferred on both cases as shown in fig3 above. They result in simultaneous or parallel statement execution.

Programming Variables in SystemVerilog: Blocking vs. Non-Blocking Assignments

Abstract: Learn the difference between blocking and non-blocking assignments in SystemVerilog and when to use each one.

SystemVerilog is a hardware description and hardware verification language used to model, design, and verify electronic systems. One of the key concepts in SystemVerilog is the use of variables and assignments. This article will focus on the two types of assignments in SystemVerilog: blocking and non-blocking assignments.

Blocking Assignments

In SystemVerilog, blocking assignments are used to assign values to program variables. A program variable is a variable that is declared using the reg or integer data type. Blocking assignments are denoted by the = symbol and are executed in order, from left to right.

In the above example, the value of variable a is assigned to variable b , and then the value of variable b is assigned to variable c . This type of assignment is called a blocking assignment because the assignment of the right-hand side expression to the left-hand side variable blocks the execution of any further statements until the assignment is complete.

Non-Blocking Assignments

Non-blocking assignments are used to assign values to non-program variables. A non-program variable is a variable that is declared using the logic , bit , or wire data type. Non-blocking assignments are denoted by the <= symbol and are executed simultaneously, not in order.

In the above example, the value of variable a is assigned to variable b , and the value of variable b is assigned to variable c , all at the same time. This type of assignment is called a non-blocking assignment because the assignment of the right-hand side expression to the left-hand side variable does not block the execution of any further statements.

Key Concepts

It is important to understand the key concepts of blocking and non-blocking assignments in SystemVerilog. Blocking assignments are used to assign values to program variables and are executed in order, from left to right. Non-blocking assignments are used to assign values to non-program variables and are executed simultaneously, not in order.

In general, it is recommended to use non-blocking assignments when assigning values to non-program variables, as this will ensure that the values are assigned at the same time and will not cause any race conditions. Blocking assignments should be used when assigning values to program variables, as this will ensure that the assignments are executed in order.

- SystemVerilog uses blocking and non-blocking assignments to assign values to variables.

- Blocking assignments are used to assign values to program variables and are executed in order.

- Non-blocking assignments are used to assign values to non-program variables and are executed simultaneously.

- It is recommended to use non-blocking assignments when assigning values to non-program variables and blocking assignments when assigning values to program variables.

- SystemVerilog LRM

- EDA Playground

- Verilog.com

--end article--

Please note that the above HTML code is properly formatted and validated.

Explore the implications of blocking and non-blocking assignments on program variables and non-program variables in SystemVerilog.

Dynamic responsive font-size based text length container (width & height).

This article explores how to create a dynamic responsive text container with adjustable font sizes based on text length and container width and height.

Adding New Headers to an Existing CSV File with Already Defined Headers

Learn how to add new headers to an existing CSV file while preserving the existing headers.

Google Play Console Account Verification: Unable to Verify Phone Number - Try Later

Learn how to handle the 'Unable to Verify Phone Number - Try Later' error during Google Play Console account verification.

Tags: : SystemVerilog Programming Assigned

Latest news

- Python Hand Detection using MediaPipe and OpenCV

- Running Unit Test Projects with Azure App Configuration in Azure DevOps Pipeline

- Docker Compose: One Replica Not Available Error

- Automating Java Jar App Tests with OpenShell and Integrated Browser

- Compiling R 4.4.1 on AlmaLinux 9.4: A Docker Container Approach

- Changing Double Format to Int64 in Power BI: Memory Occupied Column Decreases, Total File Size Increases

- AgoraCloudRecordingAPI: File Name Prefix Validation Failed Error

- Interface MQ-135 Air Quality Sensor with Raspberry Pi 4: Analog Pin Issue

- Fixing Layout Issues in an Old Web Application: Figures and Widths

- Solving ConnectionRefusedError in Flask's RestPassword

- MVN Clean Install with PostgreSQL 14/16 on Oracle Linux 9: Compile Failed - gcc failed

- Writing Text to Clipboard in BOLD Format using JavaScript

- Typegoose: Using Generic Class Model with Function Parameter

- Formatting RFH Headers with DataPower XSLTs in ServiceHub

- Transfer Data Between Two Power Apps Forms Connected to Different SharePoint Lists

- Implementing Cube Transition with CubeCubeEffect in Framer Motion React

- Upgrading Angular 14 to 15: Node-sass Build Error

- S3 Failure during SamDeploy Artifact Uploads: A 403 Error

- SpringShell Not Running in Interactive Mode on Windows 11: Unable to Create System Terminal

- Error Installing New Version: Notable Launch Android BeeWare Emulator

- Keep Message Boxes From Obstructing the Active Screen: A Software Development Solution

- Persistent Security Error: operation insecure in Next.js Project on iOS Devices

- Calculating Support Base: Previous Record in SQL Server

- Using Git to Clone and Interact with a Scala Project Repository

- Understanding Different Levels of Imports in Python

- Power BI Report Builder: Older Version Required for Azure SQL Database Connection with Active Directory Password

- Empty List When Getting Reviews from WooCommerce REST API

- Transcoding Bayer RAW10 to H.264 using GStreamer: A Step-by-Step Guide

- Migrating Gradle: Challenges with Protobuf Configuration in Android Application Build Files

- Configuring VSCode for NPM Installations in Restricted Networks

- Unable to Mount NFS Share on Ubuntu from Unraid Server

- Understanding pass environment Object UIViewRepresentable in Swift

- Creating a Mobile Number, Google, and Apple Login in Laravel

- Error: Not OpensharedObjectFile: No File Directory AzureML for PyTorch Extensions

- Hide Start, Stop Buttons and Progressive Bar: A Solution to Page Loading Issues

Verification Guide

SystemVerilog NonBlocking assignment

Nonblocking assignment.

- non-blocking assignment statements execute in parallel

- In the non-blocking assignment, all the assignments will occur at the same time. (during the end of simulation timestamp)

Nonblocking assignment example

In the below example, a and b are initialized with values 10 and 15 respectively, after that b is being assigned to a (a value will become 15), and value 20 is assigned to b. After assignment values expected in a and b are 15 and 20 respectively. but these values will get assigned only after the simulation time-stamp.

Simulator Output:

Nonblocking assignment example-2

In the below example, a and b are initialized with value 10 and 15 respectively. x<=a+b and y<=a+b+x value of x is sum of a (10) and b (15). -> x=10+15=25. value of y is sum of a (10) ,b(15) and x (0) -> became at current simulation time-stamp value of x=0. new value will get assigned at the end of current time stamp, and new value will be available only after the current time-stamp). therefore y=10+15+0=25;

❮ Previous Next ❯

- Stack Overflow for Teams Where developers & technologists share private knowledge with coworkers

- Advertising & Talent Reach devs & technologists worldwide about your product, service or employer brand

- OverflowAI GenAI features for Teams

- OverflowAPI Train & fine-tune LLMs

- Labs The future of collective knowledge sharing

- About the company Visit the blog

Collectives™ on Stack Overflow

Find centralized, trusted content and collaborate around the technologies you use most.

Q&A for work

Connect and share knowledge within a single location that is structured and easy to search.

Get early access and see previews of new features.

Mixing nonblocking and blocking assignments in an always_ff block of an arbiter

I'm unable to wrap my head around Example 10-3 in SystemVerilog For Design book by Stuart Sutherland (and co.).

See line 232 of :

https://code.google.com/p/vak-opensource/source/browse/trunk/hardware/systemverilog/utopia-example/squat.sv?r=185

Here is the snippet of code. My question will follow.

Specifically, my question is about the blocking assignment for breakVar and RoundRobin . I read somewhere that the variables are locally evaluated, but I can't picture in terms of gates how the logic is synthesized. Does RoundRobin get synthesized to a state register?

Most guidelines state to never mix blocking and nonblocking assignments. Is there a better way to represent something like this? Is it okay now in SystemVerilog designs to mix both types of assignments given that it is in an always_ff block?

- system-verilog

- round-robin

2 Answers 2

You should never mix blocking and nonblocking assignments to the same variable. breakVar is a temporary variable that will be synthesized into combinatorial logic because it is always written to first, then read. There is no state to be saved. RoundRobin is a local variable that is being used as both an intermediate and state variable. But because it is only accessed from within the always_ff block, there is no danger of a race condition.

A temporary variable is just a symbolic way to represent a piece of an equation. Here is a different but simpler example:

This is equivalent to writing the following (but might be harder to understand)

In the two examples above, counter will always be synthesized as a register because it is read before written. It won't matter if we used a blocking or nonblocking assignment because we never read counter after writing it. There is no race condition within this always_ff block using blocking assignment but there could be if there was another always_ff block trying to read it. Since full and brimming are written before being read, they do not have to be registered.

To summarize, a variable get synthesized as a register if any of these conditions are true

- A variable is read before being written within the same always block. Note that even if a non-blocking assignment statement appears first, the read happens first because the write get scheduled to happen later.

- Due to conditional or looping statements, a variable is sometimes read without being written

- A variable is written in an always_ff block and read outside the block.

- I'm not sure that's correct - RoundRobin in this case is a register, should really be using non-blocking assignment. – Chiggs Commented Jun 13, 2014 at 14:34

- I was half-correct - RoundRobin stores state but is also read after being written in the loop and so requires a blocking assignment... My comment was slightly misleading, but you spotted the deliberate mistake ;) – Chiggs Commented Jun 13, 2014 at 15:32

- 1 The 2 always block approach is cleaner, though it requires a little more typing. One always_comb for all blocking assignments including next_state values, and an always_ff for non-blocking assigning the states to their next_state. This allows see the D pin in wave from which is useful for debug. I find it makes ECOs easier to do and documented. According to Cliff's SNUG2003 paper on FSM , the 2-always approach gives better area and timing but I think it is really tool/version dependent. – Greg Commented Jun 13, 2014 at 17:24

- @dave_59, could you please elaborate a little on how a temporary variable is synthesized? – user12311164 Commented Oct 14, 2020 at 7:47

- 1 Updated answer. – dave_59 Commented Oct 17, 2020 at 22:18

Totally agreed with @jonathan answer.

You should always split your logic elements in always_comb block and sequential elements in always_ff block.

If you write a code that is so closely stitched together ( both combi and sequential elements in same block) even though it is correct and compliant with system verilog spec, some older versions of simulator or newer simulators being developed may infer it in wrong way.

Your code will not be clean and comprehensible to others.

Also by writing in above style you are just compacting the lines of code, even though the logic remains same. There is no sense in writing a compact code if it hampers the readability of the code.

Now as far as blocking and non-blocking statements usage is concerned, I think that debate is closed now. It is now more a rule than a guideline to use blocking statements in always_comb block and non-blocking in always_ff block.

However the answer to all your questions are explained in this superb paper by Clifford E Cummings Nonblocking Assignments in Verilog Synthesis, Coding Styles That Kill!

And if you are new to verilog/system verilog design I suggest you read all their papers, They are very useful and sets up a good base for a RTL Design Engineer.

Also it may be too much to tell here but if you are looking how to segregate your code in combi and sequential block you can have a look at code generated by bluespec

The signal names are difficult to comprehend in one go, but if you look closely the code is very neat logically and does not leave anything on the whims of simulation and synthesis tools.

- The paper you have quoted is about Verilog not SystemVerilog. – user12311164 Commented Oct 17, 2020 at 6:23

- @ShashankVM SystemVerilog is a superset of Verilog, same concepts apply. – nincompoop_ Commented Oct 17, 2020 at 8:43

- compliant with system verilog spec, some older versions of simulator or newer simulators being developed may infer it in wrong way then that's a bug and order the vendor to fix it ASAP, they must follow the specs or they call it something else. That's also a sufficient legal fault to invalidate any purchase of such a simulator. (done it and we won) – None Commented Apr 1, 2022 at 3:23

Your Answer

Reminder: Answers generated by artificial intelligence tools are not allowed on Stack Overflow. Learn more

Sign up or log in

Post as a guest.

Required, but never shown

By clicking “Post Your Answer”, you agree to our terms of service and acknowledge you have read our privacy policy .

Not the answer you're looking for? Browse other questions tagged system-verilog fsm synthesis round-robin or ask your own question .

- Featured on Meta

- Announcing a change to the data-dump process

- Site maintenance - Tuesday, July 23rd 2024, 8 PM - Midnight EST (3 AM - 7 AM...

- What makes a homepage useful for logged-in users

Hot Network Questions

- Event viewer showing 'logon' events, even when I'm currently using that PC

- Who were the oldest US Presidential nominees?

- Why is the future perfect used in "This latest setback will have done nothing to quell the growing doubts about the future of the club."?

- Does the "anti-dynasty" provision of the Philippines have parallels in other countries?

- Could there be another relative language of the ancient Egyptian language closer to it than the Coptic?

- What is this huge mosquito looking insect?

- Trump’s use of the term deportation

- Is "avoid extra null pointer risk" a reason to avoid "introduce parameter objects"?

- How deep should I check references of a papers I am going to cite?

- Three kilometers (~2 miles high) tsunamis go around the Earth - what kinds of ruins are left?

- "One-time discount" fraud: is any crime committed?

- Probability for a random variable to exceed its expectation

- determine whether the fundamental group of a Mobius band glued to a torus is abelian

- Whence comes the expression ‘’starve a cold, feed a fever?”

- Is there any way to save an inbred human population that also happens to be the last one left?

- Does Event Viewer have any sensitive information like password, or such info?

- Particles and fields

- Diagonal ice tunneling rover to reach a safe pressure in Mars?

- MLE for the logistic distribution

- How do I distinguish between "e" the natural log base and a variable conventionally referred to as "e"?

- Can trusted timestamping be faked by altering some bytes within the document?

- Rudimentary black jack game implementation

- How did the NES's RP2A03 noise generator generator produce 32k bit long sequences despite only being 15 bits wide?

- How far can an AC signal actually go?

IMAGES

VIDEO

COMMENTS

Blocking assignment blocks the execution of the next statement until the completion of the current assignment execution. Blocking assignment example. In Below Example, a and b is initialized with value 10 and 15 respectively, after that b is being assigned to a (a value will become 15), and value 20 is assigned to b. After assignment value of a ...

The RHS of every non-blocking statement of a particular time-step is captured, and moves onto the next statement. The captured RHS value is assigned to the LHS variable only at the end of the time-step. Simulation Log. ncsim> run. [0] a= 0xx b= 0xx c= 0xx. [0] a= 0xx b= 0xx c= 0xx. [0] a= 0xx b= 0xx c= 0xx.

Evaluate b&(~c) but defer assignment of z 1. Evaluate a | b, assign result tox x 2. Evaluate a^b^c, assign result to y 3. Evaluate b&(~c), assign result to zz I. Blocking vs. Nonblocking Assignments • Verilog supports two types of assignments within always blocks, with subtly different behaviors. • Blocking assignment: evaluation and ...

The Blocking assignment immediately takes the value in the right-hand-side and assigns it to the left hand side. Here's a good rule of thumb for Verilog: In Verilog, if you want to create sequential logic use a clocked always block with Nonblocking assignments. If you want to create combinational logic use an always block with Blocking ...

The procedural assignments can also be placed directly inside a module while declaring a variable. (Ex. reg [3:0] i_data = 4'h7) There are two types of procedural assignments and both of them are widely used in the designs written in the Verilog language. Blocking assignments; Non-blocking assignments

The conventional Verilog wisdom has it all wrong. There is no problem with using blocking assignments for a local variable. However, you should never use blocking assignments for synchronous communication, as this is nondeterministic. A non-blocking assignment within a clocked always block will always infer a flip-flop, as dictated by the ...

end. 26. end. 27. endmodule. Log. Share. 3030 views and 1 likes. This example demonstrates the use of blocking and nonblocking assignments.

Blocking and Non-blocking Assignment in Verilog. When working with behavioural modeling in Verilog, there are two types of assigment which is known as blocking and non blocking assigment and both of them there is a operator, '=' operator for blocking assignment and '=' operator for non blocking assigment.At short, blocking assignment executes one by one sequentially and non-blocking assignemnt ...

An edge-sensitive intra-assignment timing control permits a special use of the repeat loop. The edge sensitive time control may be repeated several times before the delay is completed. Either the blocking or the non-blocking assignment may be used. always always @(IN) @(IN) OUT OUT <= <= repeat.

Blocking And Nonblocking In Verilog. Blocking Statements: A blocking statement must be executed before the execution of the statements that follow it in a sequential block. In the example below the first time statement to get executed is a = b followed by. Nonblocking Statements: Nonblocking statements allow you to schedule assignments without ...

Well, "=" is blocking assignment and "<=" is nonblocking assignment. "=" executes code sequentially inside a begin / end, whereas nonblocking "<=" executes in parallel. I was fairly sure that nonblocking assignments were sequential while blocking assignments were parallel.

Blocking vs Non-Blocking Cont • Non-blocking assignments literally do not blockthe execution of the next statements. The right side of all statements are determined first, then the left sides are assigned together. - Consequently, non-blocking assignments result in simultaneous or parallel statement execution. For example: assume a = b = 0 ...

Blocking assignments. Blocking assignments (=) are done sequentially in the order the statements are written. A second assignment is not started until the preceding one is complete. i.e, it blocks all the further execution before it itself gets executed. Example: Non-Blocking assignments.

Non-blocking assignments were created to help model sequential logic. They help distinguish between the old and new value of a signal. They should be avoided in combinatorial logic as they can create problems with simulation if there are multiple clock domains. It also creates a lot of unnecessary signal rippling.

20 October 2020. Blocking / Non-Blocking assignment rules. The main reason to use either Blocking or Non-Blocking assignments is to generate either combinational or sequential logic. In non-blocking assignments (<=), all registers inside the always block are updated at the end. In blocking assignments (=), the registers are updated immediately.

In Verilog, blocking and non-blocking assignments are two different ways to assign values to variables.A blocking assignment, represented by the "=" sign, as...

This article will focus on the two types of assignments in SystemVerilog: blocking and non-blocking assignments. Blocking Assignments. In SystemVerilog, blocking assignments are used to assign values to program variables. A program variable is a variable that is declared using the reg or integer data type. Blocking assignments are denoted by ...

From Systemverilog LRM: Program variables can only be assigned using blocking assignments. Non-program variables can only be assigned using nonblocking assignments. Using nonblocking assignments with

Nonblocking assignment example. In the below example, a and b are initialized with values 10 and 15 respectively, after that b is being assigned to a (a value will become 15), and value 20 is assigned to b. After assignment values expected in a and b are 15 and 20 respectively. but these values will get assigned only after the simulation time ...

You should never mix blocking and nonblocking assignments to the same variable.breakVar is a temporary variable that will be synthesized into combinatorial logic because it is always written to first, then read. There is no state to be saved.RoundRobin is a local variable that is being used as both an intermediate and state variable. But because it is only accessed from within the always_ff ...